# PAMS Technical Documentation NHM–7 Series Transceivers

# System Module & UI

# CONTENTS

| Transceiver NHM-7                                   | 6  |

|-----------------------------------------------------|----|

| Introduction                                        | 6  |

| Electrical Modules                                  | 6  |

| Operation Modes                                     | 7  |

| Interconnection Diagram                             | 7  |

| System Module                                       | 8  |

| Baseband Module                                     | 8  |

| Block Diagram                                       | 8  |

| Technical Summary                                   | 9  |

| DC Characteristics                                  | 10 |

| Regulators and Supply Voltage Ranges                | 10 |

| External and Internal Signals and Connections       | 11 |

| Internal Signals and Connections                    | 11 |

| FM Radio Interface                                  | 11 |

| Internal microphone                                 | 12 |

| Internal speaker                                    | 12 |

| AC and DC Characteristics of RF–BB voltage supplies | 13 |

| AC and DC Characteristics of RF–BB digital signals  | 14 |

| AC and DC Characteristics of RF–BB analogue signals | 15 |

| External Signals and Connections                    | 16 |

| UI (board-to-board) connector                       | 16 |

| LCD connector                                       | 17 |

| DC connector                                        | 18 |

| Headset connector                                   | 18 |

| SIM connector                                       | 19 |

| Functional Description                              | 20 |

| Modes of Operation                                  | 20 |

| Supply Voltage Regulation                           | 21 |

| Battery                                             | 22 |

| Power Up and Reset                                  | 22 |

| A/D Channels                                        | 23 |

| FM Radio                                            | 24 |

| IR Module                                           | 25 |

| Backup Battery                                      | 25 |

| SIM Interface                                       | 25 |

| Buzzer                                              | 26 |

| Internal Microphone                                 | 26 |

|                                                     | 27 |

| Memory Block                                        | 27 |

| RF Module                                           | 29 |

| RF Frequency Plan                                   | 29 |

| DC characteristics                                  | 30 |

| Regulators                                          | 30 |

| Power Distribution Diagram                          | 31 |

| RF characteristics<br>Transmitter characteristics<br>Receiver characteristics | 32<br>32<br>32 |

|-------------------------------------------------------------------------------|----------------|

| RF Block Diagram                                                              | 33             |

| Frequency synthesizers                                                        | 34             |

| Receiver                                                                      | 35             |

| Transmitter                                                                   | 36             |

| AFC function                                                                  | 36             |

| DC-compensation                                                               | 37             |

| UI Board                                                                      | 38             |

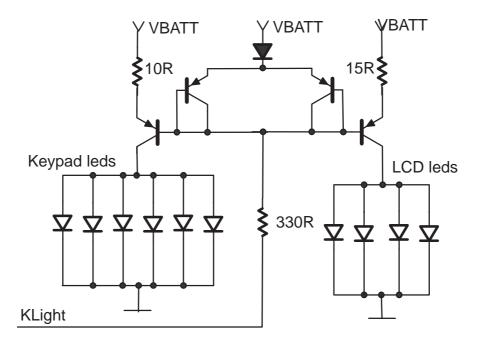

| LCD & Keypad Illumination                                                     | 38             |

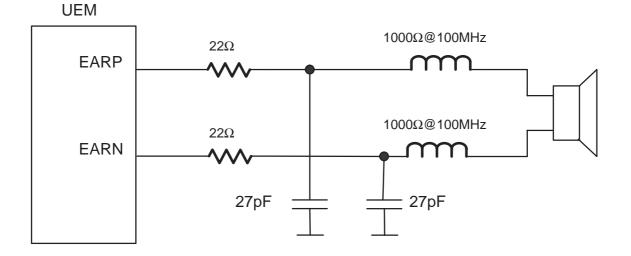

| Internal Speaker                                                              | 39             |

Schematic Diagrams (at the back of the binder): LA5 layout 15 and LK5 layout 11 (covers layout version 10)

| RF & BB (Version 0.0 Edit 61) for layout version 15                        | A–1   |

|----------------------------------------------------------------------------|-------|

| RF (Version 1.0 Edit 167) for layout version 15                            | A–2   |

| BB Connections (Version 0.0 Edit 96) for layout version 15                 | A–3   |

| System Connector (Version 1.3 Edit 156) for layout version 15              | A-4   |

| Audio Interface (Version 1.3 Edit 15) for layout version 15                | A–5   |

| UEM of BB (Version 2.0 Edit 164) for layout version 15                     | A–6   |

| Light Filtering (Version 2.0 Edit 34) for layout version 15                | A–7   |

| Display and Keyboard Interface (Version 1.3 Edit 201) for layout version 1 | 5 A8  |

| Infrared Module (Version 2.0 Edit 37) for layout version 15                | A–9   |

| FM Radio (Version 1.3 Edit 104) for layout version 15                      | A–10  |

| SIM Reader (Version 4.0.1 Edit 49) for layout version 15                   | A–11  |

| UPP and decoupling capacitors (Version 2.0 Edit 89) for layout version 1   | 5A–12 |

| AMD (Version 2.0 Edit 31) for layout version 15                            | A–13  |

| Layout Diagram of LA5 – Top (Version 15)                                   | A–14  |

| Layout Diagram of LA5 – Bottom (Version 15)                                | A–14  |

| Testpoints of LA5 – Top (Version 15)                                       | A–15  |

| Testpoints of LA5 – Bottom (Version 15)                                    | A–15  |

| UI Board – LK5 for version 11                                              | A–16  |

| Layout Diagram – LK5 for version 11                                        | A–17  |

Schematic Diagrams (at the back of the binder): LA5 layout 17 and LK5 layout 11 (covers layout version 10)

| RF & BB (Version 0.0 Edit 65) for layout version 17                        | B–1   |

|----------------------------------------------------------------------------|-------|

| RF (Version 1.0 Edit 180) for layout version 17                            | B–2   |

| BB Connections (Version 0.0 Edit 113) for layout version 17 .              | B–3   |

| System Connector (Version 1.3 Edit 162) for layout version 17              | B–4   |

| Audio Interface (Version 1.3 Edit 80) for layout version 17                | B–5   |

| UEM of BB (Version 2.0 Edit 168) for layout version 17                     | B–6   |

| Light Filtering (Version 2.0 Edit 34) for layout version 17                | B–7   |

| Display and Keyboard Interface (Version 1.3 Edit 210) for layout version 1 | 7 B–8 |

| Infrared Module (Version 2.0 Edit 38) for layout version 17                | B–9   |

| FM Radio (Version 1.3 Edit 110) for layout version 17                      | B–10  |

| SIM Reader (Version 1.3 Edit 48) for layout version 17                     | B–11  |

| UPP and decoupling capacitors (Version 2.0 Edit 91) for layout version 1   | 7B–12 |

| GSM RF – BB Interface (Version 1.3 Edit 35) for layout version 17          | B–13  |

| Flash Memory (Version 2.0 Edit 32) for layout version 17                   | B–14  |

| Layout Diagram of LA5 – Top (Version 17)                                   | B–15  |

| Layout Diagram of LA5 – Bottom (Version 17)                                | B–15  |

| Testpoints of LA5 – Top (Version xx)                                       | B–16  |

| Testpoints of LA5 – Bottom (Version 17)                                    | B–16  |

| UI Board – LK5 for version 11                                              | B–17  |

| Layout Diagram – LK5 for version 11                                        | B–18  |

This page intentionally left blank.

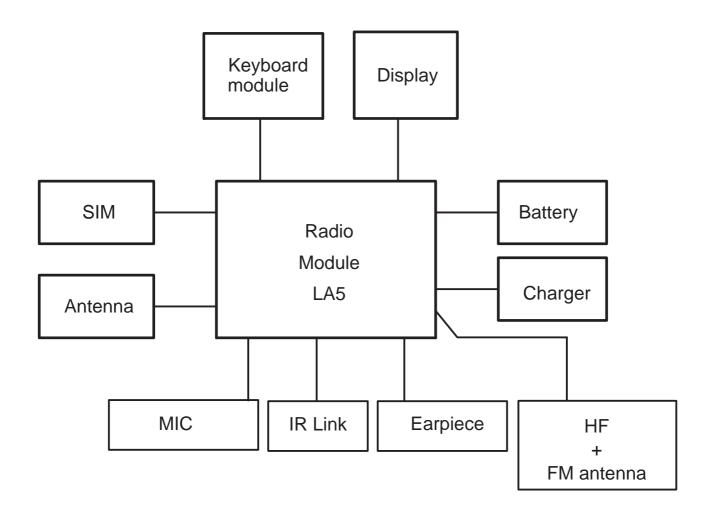

# Transceiver NHM–7

# Introduction

The NHM–7 is a dual band radio transceiver unit for the E–GSM900 and GSM1800 networks. GSM power class is 4 and GSM1800 power class is 1. It is a true 3 V transceiver, with an internal antenna and vibra.

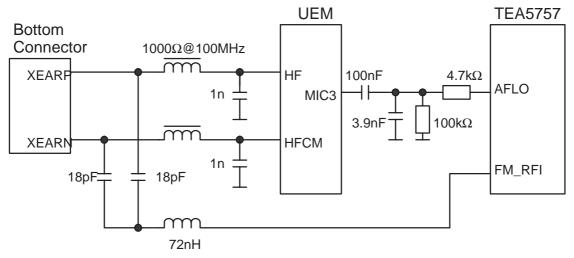

The NHM–7 phone includes integrated FM radio. Radio is used as a normal mono receiver. FM radio is highly integrated. Only few external components are needed. Headset is used as an antenna for radio.

The transceiver has a full graphic display and the user interface is based on a Jack style UI with two soft keys.

An internal antenna is used, there is no connection to an external antenna.

The transceiver has a low leakage tolerant earpiece and an omnidirectional microphone, providing an excellent audio quality. The transceiver supports a full rate, an enhanced full rate and a half rate speech decoding.

An integrated IR link provides a connection between two NHM–7 transceivers or a transceiver and a PC (internal data), or a transceiver and a printer.

The small SIM (Subscriber Identity Module) card is located under the battery. SIM interface supports both 1.8V and 3V SIM cards.

#### **Electrical Modules**

The radio module consists of Radio Frequency (RF) and baseband (BB). User Interface (UI) contains display, keyboard, IR link, vibra, HF/HS connector and audio parts. UI is divided into radio PWB LA5 and UI PWB LK5. FM radio is located on the main PWB.

The electrical part of the keyboard is located in separate UI PWB named LK5. LK5 is connected to radio PWB through spring connectors.

The System blocks provide the MCU, DSP, external memory interface and digital control functions in UPP ASIC (Universal Phone Processor). Power supply circuitry, charging, audio processing and RF control hardware are in UEM ASIC (Universal Energy Management).

The purpose of the RF block is to receive and demodulate the radio frequency signal from the base station and to transmit a modulated RF signal to the base station.

# **Operation Modes**

The transceiver has six different operation modes:

- power off mode idle mode

- active mode

charge mode

- local mode

test mode

In the power off mode circuits are powered down and only sleep clock is running.

In the idle mode only the circuits needed for power up are supplied.

In the active mode all the circuits are supplied with power although some parts might be in the idle state part of the time.

The charge mode is effective in parallel with all previous modes. The charge mode itself consists of two different states, i.e. the fast charge and the maintenance mode.

The local and test modes are used for alignment and testing.

# Interconnection Diagram

# System Module LA5

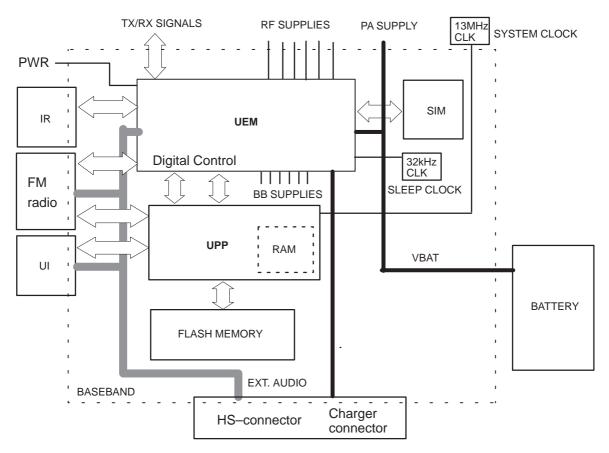

# **Baseband Module**

The baseband architecture supports a power saving function called "sleep mode". This sleep mode shuts off the VCTCXO, which is used as system clock source for both RF and baseband. During the sleep mode the system runs from a 32 kHz crystal. The phone is waken up by a timer running from this 32 kHz clock supply. The sleep time is determined by network parameters. Sleep mode is entered when both the MCU and the DSP are in standby mode and the normal VCTCXO clock is switched off.

NHM–7 supports both three and two wire type of Nokia chargers. Three wire chargers are treated like two wire ones. There is not separate PWM output for controlling charger but it is connected to GND inside the bottom connector. Charging is controlled by UEM ASIC (Universal Energy Management) and EM SW running in the UPP (Universal Phone Processor).

BLB-2 Li-ion battery is used as main power source for the phone.

# **Block Diagram**

UPP ASIC (Universal Phone Processor) provides the MCU, DSP, external memory interface and digital control functions. UEM ASIC (Universal Energy Management) contains power supply circuitry, charging, audio processing and RF control hardware.

# **Technical Summary**

Baseband is running from power rails 2.8V analog voltage and 1.8V I/O voltage. UPP core voltage Vcore can be lowered down to 1.0V, 1.3V and 1.5V. UEM includes 6 linear LDO (low drop-out) regulators for baseband and 7 regulators for RF. It also includes 4 current sources for biasing purposes and internal usage. UEM also includes SIM interface which has supports both 1.8V and 3V SIM cards.

Note: 5V SIM cards are no longer supported by NHM-7 baseband.

A real time clock function is integrated into the UEM which utilizes the same 32kHz clock supply as the sleep clock. A backup power supply is provided for the RTC which keeps the real time clock running when the main battery is removed. The backup power supply is a rechargeable surface mounted capacitor. The backup time with the capacitor is 30 minutes minimum.

The analog interface between the baseband and the RF section is handled by a UEM ASIC. UEM provides A/D and D/A conversion of the inphase and quadrature receive and transmit signal paths and also A/D and D/A conversions of received and transmitted audio signals to and from the user interface. The UEM supplies the analog TXC and AFC signals to RF section according to the UPP DSP digital control. Data transmission between the UEM and the UPP is implemented using two serial busses, DBUS for DSP and CBUS for MCU. RF ASIC, Hagar, is controlled through UPP RFBUS serial interface. There is also separate signals for PDM coded audio. Digital speech processing is handled by the DSP inside UPP ASIC. UEM is a dual voltage circuit, the digital parts are running from the baseband supply 1.8V and the analog parts are running from the analog supply 2.78V also VBAT is directly used by some blocks.

The baseband supports both internal and external microphone inputs and speaker outputs. UEM also includes third microphone input which is used in NHM–7 for FM radio. Input and output signal source selection and gain control is done by the UEM according to control messages from the UPP. Keypad tones, DTMF, and other audio tones are generated and encoded by the UPP and transmitted to the UEM for decoding. A buzzer and external vibra alert control signals are generated by the UEM with separate PWM outputs.

NHM–7 has two external serial control interfaces: FBUS and MBUS. These busses can be accessed only through production test pattern.

EMC shielding for baseband is implemented using a metallized plastic frame and UI PWB ground plane. On the other side the engine is shielded with PWB grounding. Heat generated by the circuitry will be conducted out via the PWB ground planes.

NHM–7 radio module is implemented to 8 layer PWB. UI module is divided between main PWB LA5 and separate UI PWB LK5.

# **DC Characteristics**

#### **Regulators and Supply Voltage Ranges**

#### **Battery Voltage Range**

| Signal | Min  | Nom  | Мах                                | Note            |  |

|--------|------|------|------------------------------------|-----------------|--|

| VBAT   | 3.1V | 3.6V | 4.2V (charging high limit voltage) | 3.1V SW cut off |  |

#### **BB** Regulators

| Signal  | Min                                | Nom                            | Мах                                  | Note                                                                                |

|---------|------------------------------------|--------------------------------|--------------------------------------|-------------------------------------------------------------------------------------|

| VANA    | 2.70V                              | 2.78V                          | 2.86V                                | I <sub>max</sub> = 80mA                                                             |

| VFLASH1 | 2.70V                              | 2.78V                          | 2.86V                                | I <sub>max</sub> = 70mA<br>I <sub>Sleep</sub> = 1.5mA                               |

| VFLASH2 | 2.70V                              | 2.78V                          | 2.86V                                | I <sub>max</sub> = 40mA                                                             |

| VSIM    | 1.745V<br>2.91V                    | 1.8V<br>3.0V                   | 1.855V<br>3.09V                      | I <sub>max</sub> = 25mA<br>I <sub>Sleep</sub> = 0.5mA                               |

| VIO     | 1.72V                              | 1.8V                           | 1.88V                                | I <sub>max</sub> = 150mA<br>I <sub>Sleep</sub> = 0.5mA                              |

| VCORE   | 1.0V<br>1.235V<br>1.425V<br>1.710V | 1.053V<br>1.3V<br>1.5V<br>1.8V | 1.106V<br>1.365V<br>1.575V<br>1.890V | $I_{max} = 200 \text{mA}$<br>$I_{Sleep} = 0.2 \text{mA}$<br>Default value =<br>1.5V |

#### **RF Regulators**

| Signal | Min            | Nom           | Мах            | Note                       |

|--------|----------------|---------------|----------------|----------------------------|

| VR1A   | 4.6V           | 4.75V         | 4.9V           | I <sub>max</sub> = 10mA    |

| VR2    | 2.70V<br>3.20V | 2.78V<br>3.3V | 2.86V<br>3.40V | I <sub>max</sub> = 100mA   |

| VR3    | 2.70V          | 2.78V         | 2.86V          | I <sub>max</sub> = 20mA    |

| VR4    | 2.70V          | 2.78V         | 2.86V          | I <sub>max</sub> = 50mA    |

|        |                |               |                | I <sub>Sleep</sub> = 0.1mA |

| VR5    | 2.70V          | 2.78V         | 2.86V          | I <sub>max</sub> = 50mA    |

|        |                |               |                | I <sub>Sleep</sub> = 0.1mA |

| VR6    | 2.70V          | 2.78V         | 2.86V          | I <sub>max</sub> = 50mA    |

|        |                |               |                | I <sub>Sleep</sub> = 0.1mA |

| VR7    | 2.70V          | 2.78V         | 2.86V          | I <sub>max</sub> = 45mA    |

# **External and Internal Signals and Connections**

This section describes the external and internal electrical connection and interface levels on the baseband. The electrical interface specifications are collected into tables that covers a connector or a defined interface.

# **Internal Signals and Connections**

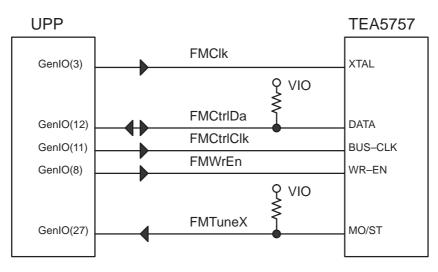

#### **FM** Radio Interface

| BB Signal | FM Radio<br>Signal | Min        | Nom      | Max           | Condition                       | Note                                                                                         |

|-----------|--------------------|------------|----------|---------------|---------------------------------|----------------------------------------------------------------------------------------------|

| VFLASH2   | Vcc1               | 2.7V       | 2.78V    | 2.86V         |                                 | max. lcc1<br>19mA                                                                            |

|           | Vcc2               | 2.7V       | 2.78V    | 2.86V         |                                 | max. lcc2<br>800uA                                                                           |

|           | VDD                | 2.7V       | 2.78V    | 2.86V         |                                 | max. IDD<br>3mA                                                                              |

| GenIO(3)  | FMClk              | 1.4V<br>0  | 1.8V     | 1.88V<br>0.4V | High<br>Low                     | Reference<br>clock for FM<br>radio module                                                    |

|           |                    |            | 76471 Hz |               | Frequency                       | In GSM                                                                                       |

|           |                    | 30ppm      |          |               | Stability                       |                                                                                              |

|           |                    |            |          | 2 μs          | t <sub>rise</sub>               | rise / fall time                                                                             |

| GenIO(8)  | FMWrEn             | 1.4V<br>0V | 1.8V     | 1.88V<br>0.4V | High<br>Low                     |                                                                                              |

|           |                    | 20µs       |          |               | t <sub>wd</sub>                 | <i>FMWrEn</i> high<br>before rising<br>edge of<br><i>FMCtrIClk</i><br>(write opera-<br>tion) |

| GenIO(11) | FMCtrlClk          | 1.4V<br>0  | 1.8V     | 1.88V<br>0.4V | High<br>Low                     | max. 300kHz                                                                                  |

|           |                    |            |          | 1 μs          | t <sub>r</sub> / t <sub>f</sub> | rise / fall time                                                                             |

|           |                    | 50 ms      |          |               | t <sub>start</sub>              | <i>FMCtrIClk</i><br>delay after<br>switching on<br>the VFLASH2<br>(oscillator run-<br>ning)  |

| BB Signal | FM Radio<br>Signal | Min                 | Nom                 | Мах                 | Condition           | Note                                                                                              |

|-----------|--------------------|---------------------|---------------------|---------------------|---------------------|---------------------------------------------------------------------------------------------------|

| GenIO(12) | FMCtrlDa           | 1.4V<br>0           | 1.8V                | 1.88V<br>0.4V       | High<br>Low         | Bidirectional                                                                                     |

|           |                    |                     |                     | 14us                | t <sub>da</sub>     | shift register<br>available after<br>"search<br>ready"                                            |

|           |                    | 10 µs               |                     |                     | t <sub>shift</sub>  | data available<br>after<br><i>FMCtrIClk</i> ris-<br>ing edge (read<br>operation)                  |

|           |                    | 1.5 μs              |                     |                     | t <sub>hold</sub>   | <i>FMCtrIDa</i> sta-<br>bile after<br><i>FMCtrIClk</i> ris-<br>ing edge<br>(write opera-<br>tion) |

| GenIO(27) | FMTuneX            | 1.4V<br>0           | 1.8V                | 1.88V<br>0.4V       | High<br>Low         | from FM mod-<br>ule to UPP<br>(FMCtrlClk =<br>'1')                                                |

| MIC3P     | FMAudio            | 228mV <sub>pp</sub> | 326mV <sub>pp</sub> | 460mV <sub>pp</sub> |                     |                                                                                                   |

|           |                    | 50dB                |                     |                     | S/N                 |                                                                                                   |

|           |                    |                     |                     | 2%                  | Harmonic distortion |                                                                                                   |

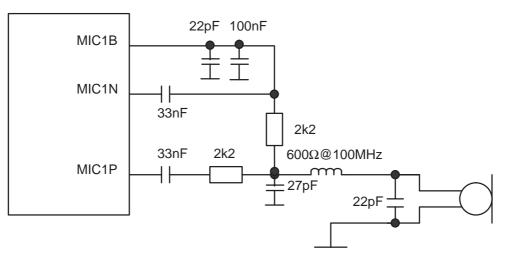

# Internal microphone

| Signal | Min   | Nom Max |                     | Condition | Note            |

|--------|-------|---------|---------------------|-----------|-----------------|

| MICP   |       |         | 200mV <sub>pp</sub> | AC        | $2.2k\Omega$ to |

|        | 2.0 V | 2.1 V   | 2.25 V              | DC        | MIC1B           |

| MICN   | 2.0V  | 2.1V    | 2.25V               | DC        |                 |

#### Internal speaker

| Signal | Min   | Nom  | Max                 | Condition | Note                                          |

|--------|-------|------|---------------------|-----------|-----------------------------------------------|

| EARP   |       |      | 2.0 V <sub>pp</sub> | AC        |                                               |

|        | 0.75V | 0.8V | 0.85V               | DC        | Differential<br>output                        |

| EARN   |       |      | 2.0 V <sub>pp</sub> | AC        |                                               |

|        | 0.75V | 0.8V | 0.85V               | DC        | (V <sub>diff</sub> = 4.0<br>V <sub>pp</sub> ) |

# AC and DC Characteristics of RF–BB voltage supplies

| Signal<br>name | From    | То           | Parameter                                               | Min  | Тур  | Max               | Unit               | Function                                                                                                         |

|----------------|---------|--------------|---------------------------------------------------------|------|------|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------|

| VBAT           | Battery | PA & UEM     | Voltage                                                 | 2.95 | 3.6  | 4.2               | V                  | Battery supply.<br>Cut–off level of<br>DCT4 regulators is                                                        |

|                |         |              | Current                                                 |      |      | 2000              | mA                 | 3.04V. Losses in<br>pcb tracks and<br>ferrites are taken<br>account to minimum<br>battery voltage<br>level.      |

|                |         |              | Current drawn by PA when "off"                          |      | 0.8  | 2                 | uA                 |                                                                                                                  |

| VR1A           | UEM     | VCP          | Voltage                                                 | 4.6  | 4.75 | 4.9               | V                  | Supply for varactor                                                                                              |

|                |         |              | Current                                                 |      | 2    | 10                | mA                 | for UHF VCO<br>tuning.                                                                                           |

|                |         |              | Noise density                                           |      |      | 240               | nVrms/<br>sqrt(Hz) |                                                                                                                  |

| VR2            | UEM     | VRF_TX       | Voltage                                                 | 2.70 | 2.78 | 2.86              | V                  | Supply for part of                                                                                               |

|                |         |              | Current                                                 |      | 65   | 100               | mA                 | transmit strip.<br>Supply for TX                                                                                 |

|                |         |              | Noise density<br>f=100Hz<br>f>300Hz                     |      |      | 120               | nVrms/<br>sqrt(Hz) | I/Q-modulators.                                                                                                  |

| VR3            | UEM     | VCTCXO       | Voltage                                                 | 2.70 | 2.78 | 2.86              | V                  | Supply for VCTCXO                                                                                                |

|                |         |              | Current                                                 |      | 1    | 20                | mA                 |                                                                                                                  |

|                |         |              | Noise density                                           |      |      | 240               | nVrms/<br>sqrt(Hz) |                                                                                                                  |

| VR4            | UEM     | VRF_RX       | Voltage                                                 | 2.70 | 2.78 | 2.86              | V                  | Supply for Hagar<br>RX; preamp., mixer,                                                                          |

|                |         |              | Current                                                 |      |      | 50                | mA                 | DTOS<br>Noise density                                                                                            |

|                |         |              | Noise density<br>f = 6 Hz<br>f = 60 Hz<br>$f \ge 600Hz$ |      |      | 5500<br>550<br>55 | nVrms/<br>sqrt(Hz) | decades 20dB/dec<br>from 6Hz to 600Hz.<br>From f >600Hz<br>maximum noise<br>density<br>55nV <sub>RMS</sub> /√Hz. |

| VR5            | UEM     | VDIG,        | Voltage                                                 | 2.70 | 2.78 | 2.86              | V                  | Supply for Hagar                                                                                                 |

|                |         | VPRE,<br>VLO | Current                                                 |      |      | 50                | mA                 | PLL; dividers, LO–<br>buffers, prescaler,                                                                        |

|                |         |              | Noise density<br>BW=100Hz<br>100kHZ                     |      |      | 240               | nVrms/<br>sqrt(Hz) |                                                                                                                  |

| VR6            | UEM     | VBB          | Voltage                                                 | 2.70 | 2.78 | 2.86              | V                  | Supply for Hagar                                                                                                 |

|                |         |              | Current                                                 |      |      | 50                | mA                 | BB and LNA                                                                                                       |

|                |         |              | Noise density<br>BW=100Hz<br>100kHz                     |      |      | 240               | nVrms/<br>sqrt(Hz) |                                                                                                                  |

| Signal<br>name | From | То      | Parameter                                                                                                                                                                                                                                                           | Min   | Тур  | Max                        | Unit               | Function                                    |

|----------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|----------------------------|--------------------|---------------------------------------------|

| VR7            | UEM  | UHF VCO | Voltage                                                                                                                                                                                                                                                             | 2.70  | 2.78 | 2.86                       | V                  | Supply for UHF                              |

|                |      |         | Current                                                                                                                                                                                                                                                             |       |      | 30                         | mA                 | VCO                                         |

|                |      |         | Noise density<br>100Hz <f<2khz<br>2kHz<f<10khz<br>10kHz<f<30khz<br>30kHz<f<90khz<br>90kHz<f<3mhz< td=""><td></td><td></td><td>70<br/>55<br/>35<br/>30<br/>30</td><td>nVrms/<br/>sqrt(Hz)</td><td></td></f<3mhz<></f<90khz<br></f<30khz<br></f<10khz<br></f<2khz<br> |       |      | 70<br>55<br>35<br>30<br>30 | nVrms/<br>sqrt(Hz) |                                             |

| VrefRF01       | UEM  | VREF_RX | Voltage                                                                                                                                                                                                                                                             | 1.334 | 1.35 | 1.366                      | V                  | Voltage Reference                           |

|                |      |         | Current                                                                                                                                                                                                                                                             |       |      | 100                        | uA                 | for RF–IC.                                  |

|                |      |         | Temp Coef                                                                                                                                                                                                                                                           | -65   |      | +65                        | uV/C               | Note: Below<br>600Hz noise<br>density is    |

|                |      |         | Noise density<br>BW=600Hz<br>100kHz <b>Note</b>                                                                                                                                                                                                                     |       |      | 60                         | nVrms/<br>sqrt(Hz) | allowed to<br>increase 20<br>dB/oct         |

| VrefRF02       | UEM  | VB_EXT  | Voltage                                                                                                                                                                                                                                                             | 1.323 | 1.35 | 1.377                      | V                  | Supply for RF–BB                            |

|                |      |         | Current                                                                                                                                                                                                                                                             |       |      | 100                        | uA                 | digital interface and some digital parts of |

|                |      |         | Temp Coef                                                                                                                                                                                                                                                           | -65   |      | +65                        | uV/C               | RF.                                         |

|                |      |         | Noise density<br>BW=100Hz<br>100kHz                                                                                                                                                                                                                                 |       |      | 350                        | nVrms/<br>sqrt(Hz) |                                             |

# AC and DC Characteristics of RF–BB digital signals

| Cirmel neme        | From | To            | Devementer       | In   | put Cha | racteris | tics   | Fun                    |

|--------------------|------|---------------|------------------|------|---------|----------|--------|------------------------|

| Signal name        | From | То            | Parameter        | Min  | Тур     | Мах      | Unit   | Fun<br>c-<br>tion      |

| TXP<br>(RFGenOut3) | UPP  | PA &<br>RF–IC | "1"              | 1.38 |         | 1.88     | V      | Tran<br>smit<br>ter    |

|                    |      |               | "O"              | 0    |         | 0.4      | V      | pow<br>er<br>amp       |

|                    |      |               | Load Resistance  | 10   |         | 220      | kohm   | lifier<br>ena<br>ble / |

|                    |      |               | Load Capacitance |      |         | 20       | pF     | DC<br>N2<br>timi       |

|                    |      |               | Timing Accuracy  |      |         | 1/4      | symbol | ng?<br>??              |

NOKIA PAMS Technical Documentation

| Signal name | From | То    | Parameter        |      |     |      |        | <u>Fun</u>    |

|-------------|------|-------|------------------|------|-----|------|--------|---------------|

|             |      |       |                  | Min  | Тур | Max  | Unit   | c-<br>tion    |

| RFBusEna1X  | UPP  | RF–IC | "1"              | 1.38 |     | 1.88 | V      | RFb           |

|             |      |       | "0"              | 0    |     | 0.4  | V      | us<br>ena     |

|             |      |       | Current          |      |     | 50   | uA     | ble           |

|             |      |       | Load resistance  | 10   |     | 220  | kohm   |               |

|             |      |       | Load capacitance |      |     | 20   | pF     |               |

| RFBusData   | UPP  | RF–IC | "1"              | 1.38 |     | 1.88 | V      | RFb           |

|             |      |       | "0"              | 0    |     | 0.4  | V      | us<br>data    |

|             |      |       | Load resistance  | 10   |     | 220  | kohm   | ;             |

|             |      |       | Load capacitance |      |     | 20   | pF     | read<br>/writ |

|             |      |       | Data frequency   |      |     | 10   | MHz    | е             |

| RFBusClk    | UPP  | RF–IC | "1"              | 1.38 |     | 1.88 | V      | RFb           |

|             |      |       | "0"              | 0    |     | 0.4  | V      | us<br>cloc    |

|             |      |       | Load resistance  | 10   |     | 220  | kohm   | k             |

|             |      |       | Load capacitance |      |     | 20   | pF     |               |

|             |      |       | Data frequency   |      |     | 10   | MHz    |               |

| RESET       | UPP  | RF–IC | "1"              | 1.38 |     | 1.85 | V      | Res           |

| (GENIO6)    |      |       | "0"              | 0    |     | 0.4  | V      | et to<br>Hag  |

|             |      |       | Load capacitance |      |     | 20   | pF     | ar            |

|             |      |       | Load resistance  | 10   |     | 220  | kohm   |               |

|             |      |       | Timing accuracy  |      |     | 1/4  | symbol |               |

# AC and DC Characteristics of RF–BB analogue signals

| Signal name | From   | То  | Parameter                           | Min  | Тур  | Max  | Unit | Function                          |

|-------------|--------|-----|-------------------------------------|------|------|------|------|-----------------------------------|

| VCTCXO      | VCTCXO | UPP | Signal amplitude                    | 0.2  | 0.8  | 2.0  | Vpp  | High stability clock              |

|             |        |     | Input Impedance                     | 10   |      |      | kohm | signal for the logic circuits, AC |

|             |        |     | Input Capacitance                   |      |      | 10   | pF   | coupled. Distorted                |

|             |        |     | Harmonic Content                    |      |      | -8   | dBc  | sine wave eg.<br>sawtooth.        |

|             |        |     | Clear signal<br>window (no glitch)  | 200  |      |      | mVpp |                                   |

|             |        |     | Duty Cycle                          | 40   |      | 60   | %    |                                   |

| VCTCXOGnd   | VCTXO  | UPP | DC Level                            |      | 0    |      | V    | Ground for<br>reference clock     |

| RXI/RXQ     | RF–IC  | UEM | Differential voltage swing (static) | 1.35 | 1.4  | 1.45 | Vpp  | RX baseband signal.               |

|             |        |     | DC level                            | 1.3  | 1.35 | 1.4  | V    |                                   |

|             |        |     | I/Q amplitude<br>missmatch          |      |      | 0.2  | dB   |                                   |

|             |        |     | I/Q phase<br>missmatch              | -5   |      | 5    | deg  |                                   |

PAMS Technical Documentation

| Signal name      | From | То     | Parameter                           | Min        | Тур  | Max        | Unit                                                                              | Function                                                |

|------------------|------|--------|-------------------------------------|------------|------|------------|-----------------------------------------------------------------------------------|---------------------------------------------------------|

| TXIP / TXIN      | UEM  | RF–IC  | Differential voltage swing (static) | 2.23       |      | 2.48       | Vpp                                                                               | Programmable voltage swing.                             |

|                  |      |        | DC level                            | 1.17       | 1.20 | 1.23       | V                                                                                 | Programmable<br>common mode<br>voltage.                 |

|                  |      |        | Source<br>Impedance                 |            |      | 200        | ohm                                                                               | Between<br>TXIP-TXIN                                    |

| TXQP /<br>TXQN   | UEM  | RF–IC  | Same spec as for TXIP / TXIN        |            |      |            | Differential<br>quadrature phase<br>TX baseband<br>signal for the RF<br>modulator |                                                         |

| AFC              | UEM  | VCTCXO | Voltage Min<br>Max                  | 0.0<br>2.4 |      | 0.1<br>2.6 | V                                                                                 | Automatic<br>frequency control                          |

|                  |      |        | Resolution                          | 11         |      |            | bits                                                                              | signal for<br>VCTCXO                                    |

|                  |      |        | Load resistance<br>and capacitance  | 1          |      | 100        | kohm<br>nF                                                                        |                                                         |

|                  |      |        | Step settling time                  |            |      | 0.2        | ms                                                                                |                                                         |

| Aux_DAC<br>(TxC) | UEM  | RF     | Voltage Min<br>Max                  | 2.4        |      | 0.1        | V                                                                                 | Transmitter power control                               |

|                  |      |        | Source<br>Impedance                 |            |      | 200        | ohm                                                                               |                                                         |

|                  |      |        | Resolution                          | 10         |      |            | bits                                                                              |                                                         |

|                  |      |        | Noise density<br>BW=100Hz<br>100kHz |            |      | 800        | nVrms/<br>sqrt(Hz)                                                                | NOTE; Assumed<br>power control<br>opamp G=1             |

|                  |      |        | Temp Coef                           | -65        |      | +65        | uV/C                                                                              |                                                         |

| RFTemp           | RF   | UEM    | Voltage at –20°C                    |            | 1,57 |            | V                                                                                 | Temperature                                             |

|                  |      |        | Voltage at +25°C                    |            | 1,7  |            | 1                                                                                 | sensor of RF.                                           |

|                  |      |        | Voltage at +60°C                    |            | 1,79 |            |                                                                                   |                                                         |

| Vbase            | RF   | UEM    | Voltage                             |            |      | 2.7        | V                                                                                 | Detected voltage<br>from PA power<br>level sensing unit |

# **External Signals and Connections**

# UI (board-to-board) connector

| Pin | Signal    | Min          | Nom  | Мах             | Condition                | Note                         |

|-----|-----------|--------------|------|-----------------|--------------------------|------------------------------|

| 1   | SLOWAD(2) | 1.5V<br>0.1V |      | 2.7V<br>1.0V    | Flip closed<br>Flip open | used for flip identification |

| 2   | VBAT      | 3.0V         | 3.6V | 4.2V            |                          | Battery voltage for leds     |

| 3   | ROW(4)    | 0.7xVIO<br>0 |      | 1.8V<br>0.3xVIO | High<br>Low              | Keyboard ma-<br>trix row 4   |

| Pin | Signal | Min          | Nom | Max              | Condition         | Note                          |

|-----|--------|--------------|-----|------------------|-------------------|-------------------------------|

| 4   | ROW(3) | 0.7xVIO<br>0 |     | VIO<br>0.3xVIO   | High<br>Low       | Keyboard ma-<br>trix row 3    |

| 5   | COL(2) | 0.7xVIO<br>0 |     | VIO<br>0.3xVIO   | High<br>Low       | Keyboard ma-<br>trix column 2 |

| 6   | ROW(2) | 0.7xVIO<br>0 |     | VIO<br>0.3xVIO   | High<br>Low       | Keyboard ma-<br>trix row 2    |

| 7   | COL(1) | 0.7xVIO<br>0 |     | VIO<br>0.3xVIO   | High<br>Low       | Keyboard ma-<br>trix column 1 |

| 8   | ROW(0) | 0.7xVIO<br>0 |     | VIO<br>0.3xVIO   | High<br>Low       | Keyboard ma-<br>trix row 0    |

| 9   | KLIGHT |              |     | VBAT<br>0.3xVBAT | LED off<br>LED on | two colour led control        |

| 10  | ROW(1) | 0.7xVIO<br>0 |     | VIO<br>0.3xVIO   | High<br>Low       | Keyboard ma-<br>trix row 1    |

| 11  | COL(3) | 0.7xVIO<br>0 |     | VIO<br>0.3xVIO   | High<br>Low       | Keyboard ma-<br>trix column 3 |

| 12  | COL(4) | 0.7xVIO<br>0 |     | VIO<br>0.3xVIO   | High<br>Low       | Keyboard ma-<br>trix column 4 |

| 13  | GND    |              | 0V  |                  |                   |                               |

| 14  | GND    |              | 0V  |                  |                   |                               |

| 15  | GND    |              | 0V  |                  |                   |                               |

| 16  | GND    |              | 0V  |                  |                   |                               |

#### LCD connector

| Pin | Signal | Min     | Nom | Max      | Condition        | Note                                  |

|-----|--------|---------|-----|----------|------------------|---------------------------------------|

| 1   | XRES   | 0.8*VIO |     | VIO      | Logic '1'        | Reset                                 |

|     |        | 0       |     | 0.22*VIO | Logic '0'        | Active low                            |

|     |        | 100ns   |     |          | t <sub>rw</sub>  | Reset active                          |

| 2   | XCS    | 0.8*VIO |     | VIO      | Logic '1'        | Chip select                           |

|     |        | 0       |     | 0.22*VIO | Logic '0'        | Active low                            |

|     |        | 130ns   |     |          | t <sub>css</sub> | XCS low before<br>SCLK rising<br>edge |

|     |        | 130ns   |     |          | t <sub>csh</sub> | XCS low after<br>SCLK rising<br>edge  |

|     |        | 300ns   |     |          | t <sub>csw</sub> | XCS high pulse width                  |

| 3   | GND    |         | 0V  |          |                  |                                       |

| 4   | SDA    | 0.8*VIO |     | VIO      | Logic '1'        | Serial data                           |

|     |        | 0       |     | 0.22*VIO | Logic '0'        | (driver input)                        |

|     |        | 0.7*VIO |     | VIO      | Logic '1'        | Serial data                           |

|     |        | 0       |     | 0.3*VIO  | Logic '0'        | (driver output)                       |

|     |        | 100ns   |     |          | t <sub>sds</sub> | Data setup time                       |

|     |        | 100ns   |     |          | t <sub>sdh</sub> | Data hold time                        |

| Pin | Signal           | Min     | Nom   | Max      | Condition         | Note                                           |

|-----|------------------|---------|-------|----------|-------------------|------------------------------------------------|

| 5   | SCLK             | 0.8*VIO |       | VIO      | Logic '1'         | Serial clock in-                               |

|     |                  | 0       |       | 0.22*VIO | Logic '0'         | put                                            |

|     |                  |         |       | 4.0MHz   | Max frequency     |                                                |

|     |                  | 250ns   |       |          | t <sub>scyc</sub> | Clock cycle                                    |

|     |                  | 110ns   |       |          | t <sub>shw</sub>  | Clock high                                     |

|     |                  | 110ns   |       |          | t <sub>slw</sub>  | Clock low                                      |

| 6   | VDDI (VIO)       | 1.72V   | 1.8V  | 1.88V    |                   | Logic voltage supply                           |

|     |                  |         |       |          |                   | Connected to VIO                               |

| 7   | VDD<br>(VFLASH1) | 2.72V   | 2.78V | 2.86V    |                   | Voltage supply                                 |

|     |                  |         |       |          |                   | Connected to<br>VFLASH1                        |

| 8   | VOUT             |         |       | 9V       |                   | Booster output,<br>C=1uF con-<br>nected to GND |

#### **DC** connector

| Pin | Signal | Min                  | Nom                  | Max                            | Condition         | Note                        |

|-----|--------|----------------------|----------------------|--------------------------------|-------------------|-----------------------------|

| 2   | VCHAR  | 7.0 V <sub>RMS</sub> | 8.4 V <sub>RMS</sub> | 9.2 V <sub>RMS</sub><br>850 mA | Fast char-<br>ger | Charger posi-<br>tive input |

| 1   | CHGND  |                      | 0                    |                                |                   | Charger ground              |

#### Headset connector

| Pin | Signal  | Min   | Nom   | Max                  | Condition | Note                                  |

|-----|---------|-------|-------|----------------------|-----------|---------------------------------------|

| 5   | XMICP   |       |       | 1V <sub>pp</sub>     | G = 0 dB  | 1kΩ to MIC2B                          |

|     |         |       |       | 100 mV <sub>pp</sub> | G = 20dB  |                                       |

|     |         | 2.0 V | 2.1 V | 2.25 V               | DC        |                                       |

| 3   | XMICN   |       |       | 1V <sub>pp</sub>     | G = 0 dB  | $1k\Omega$ to GND                     |

|     |         |       |       | 100 mV <sub>pp</sub> | G = 20dB  |                                       |

| 4   | XEARN   | 0.75V | 0.8V  | 0.85V                | DC        |                                       |

|     |         |       |       | 1V <sub>pp</sub>     | AC        |                                       |

| 7   | XEARP   | 0.75V | 0.8V  | 0.85V                | DC        |                                       |

|     |         |       |       | 1V <sub>pp</sub>     | AC        |                                       |

| 5   | HookInt | 0V    |       | 2.86V<br>(VFLASH1)   |           | Connected to<br>UEM AD–con-<br>verter |

| 6   | HeadInt | 0V    |       | 2.86V<br>(VANA)      |           | Accessory<br>detection                |

# **NOKIA** PAMS Technical Documentation

#### **SIM connector**

| Pin | Name   | Parameter     | Min      | Тур  | Max       | Unit | Notes               |

|-----|--------|---------------|----------|------|-----------|------|---------------------|

| 1   | VSIM   | 1.8V SIM Card | 1.6      | 1.8  | 1.9       | V    | Supply voltage      |

|     |        | 3V SIM Card   | 2.8      | 3.0  | 3.2       |      |                     |

| 2   | SIMRST | 1.8V SIM Card | 0.9xVSIM |      | VSIM      | V    | SIM reset (output)  |

|     |        |               | 0        |      | 0.15xVSIM |      |                     |

|     |        | 3V SIM Card   | 0.9xVSIM |      | VSIM      |      |                     |

|     |        |               | 0        |      | 0.15xVSIM |      |                     |

| 3   | SIMCLK | Frequency     |          | 3.25 |           | MHz  | SIM clock           |

|     |        | Trise/Tfall   |          |      | 50        | ns   |                     |

|     |        | 1.8V Voh      | 0.9xVSIM |      | VSIM      | V    |                     |

|     |        | 1.8V Vol      | 0        |      |           |      |                     |

|     |        | 3 Voh         | 0.9xVSIM |      | VSIM      |      |                     |

|     |        | 3 Vol         | 0        |      |           |      |                     |

| 4   | DATA   | 1.8V Voh      | 0.9xVSIM |      | VSIM      | V    | SIM data (output)   |

|     |        | 1.8V Vol      | 0        |      | 0.15xVSIM |      |                     |

|     |        | 3 Voh         | 0.9xVSIM |      | VSIM      |      |                     |

|     |        | 3 Vol         | 0        |      | 0.15xVSIM |      |                     |

|     |        | 1.8V Vih      | 0.7xVSIM |      | VSIM      |      | SIM data (input)    |

|     |        | 1.8V Vil      | 0        |      | 0.15xVSIM |      | Trise/Tfall max 1us |

|     |        | 3V Vil        | 0.7xVSIM |      | VSIM      |      |                     |

|     |        | 3V Vil        | 0        |      | 0.15xVSIM |      |                     |

| 5   | NC     |               |          |      |           |      |                     |

| 6   | GND    | GND           |          | 0    |           | V    | Ground              |

# **Functional Description**

# **Modes of Operation**

LA5 baseband engine has six different operating modes:

- No supply

- Backup

- Acting Dead

- Active

- Sleep

- Charging

#### No supply

In NO\_SUPPLY mode the phone has no supply voltage. This mode is due to disconnection of main battery and backup battery or low battery voltage level in both of the batteries.

Phone is exiting from NO\_SUPPLY mode when sufficient battery voltage level is detected. Battery voltage can rise either by connecting a new battery with VBAT >  $V_{MSTR+}$  or by connecting charger and charging the battery above  $V_{MSTR+}$ .

#### Backup

In BACKUP mode the backup battery has sufficient charge but the main battery can be disconnected or empty (VBAT <  $V_{MSTR}$  and VBACK > VBU<sub>COFF</sub>).

VRTC regulator is disabled in BACKUP mode. VRTC output is supplied without regulation from backup battery (VBACK). All the other regulators are disabled.

#### **Acting Dead**

If the phone is off when the charger is connected, the phone is powered on but enters a state called "Acting Dead". To the user the phone acts as if it was switched off. A battery charging alert is given and/or a battery charging indication on the display is shown to acknowledge the user that the battery is being charged.

#### Active

In the active mode the phone is in normal operation, scanning for channels, listening to a base station, transmitting and processing information. There are several sub-states in the active mode depending on if the phone is in burst reception, burst transmission, if DSP is working etc.

One of the sub–state of the active mode is FM radio on state. In that case UEM audio blocks and FM radio are powered on. FM radio circuitry is controlled by the MCU and 75kHz reference clock is generated in the UPP. VFLASH2 regulator is operating.

In active mode the RF regulators are controlled by SW writing into UEM's registers wanted settings: VR1A can be enabled or disabled. VR2 can be enabled or disabled and its output voltage can be programmed to be

2.78V or 3.3V. VR4 –VR7 can be enabled or disabled or forced into low quiescent current mode. VR3 is always enabled in active mode.

#### Sleep mode

Sleep mode is entered when both MCU and DSP are in stand-by mode. Sleep is controlled by both processors. When SLEEPX low signal is detected UEM enters SLEEP mode. VCORE, VIO and VFLASH1 regulators are put into low quiescent current mode. All RF regulators are disabled in SLEEP. When SLEEPX=1 is detected UEM enters ACTIVE mode and all functions are activated.

The sleep mode is exited either by the expiration of a sleep clock counter in the UEM or by some external interrupt, generated by a charger connection, key press, headset connection etc.

In sleep mode VCTCXO is shut down and 32 kHz sleep clock oscillator is used as reference clock for the baseband.

#### Charging

The battery voltage, temperature, size and current are measured by the UEM controlled by the charging software running in the UPP.

The charging control circuitry (CHACON) inside the UEM controls the charging current delivered from the charger to the battery. The battery voltage rise is limited by turning the UEM switch off when the battery voltage has reached 4.2 V. Charging current is monitored by measuring the voltage drop across a 220 mOhm resistor.

#### **Supply Voltage Regulation**

Supply voltage regulation is controlled by UEM asic. There are six separate regulators used by baseband block.

#### **BB** Regulators

| Signal  | Min              | Nom          | Мах              | Note                       |

|---------|------------------|--------------|------------------|----------------------------|

| VANA    | 2.70V            | 2.78V        | 2.86V            | I <sub>max</sub> = 80mA    |

| VFLASH1 | 2.70V            | 2.78V        | 2.86V            | I <sub>max</sub> = 70mA    |

|         |                  |              |                  | I <sub>Sleep</sub> = 1.5mA |

| VFLASH2 | 2.70V            | 2.78V        | 2.86V            | $I_{max} = 40 mA$          |

| VSIM    | 1.745V           | 1.8V         | 1.855V           | I <sub>max</sub> = 25mA    |

|         | 2.91V            | 3.0V         | 3.09V            | I <sub>Sleep</sub> = 0.5mA |

| VIO     | 1.72V            | 1.8V         | 1.88V            | I <sub>max</sub> = 150mA   |

|         |                  |              |                  | I <sub>Sleep</sub> = 0.5mA |

| VCORE   | 1.0V             | 1.053V       | 1.106V           | $I_{max} = 200 \text{mA}$  |

|         | 1.235V<br>1.425V | 1.3V<br>1.5V | 1.365V<br>1.575V | I <sub>Sleep</sub> = 0.2mA |

|         | 1.710V           | 1.8V         | 1.890V           | Default value =<br>1.5V    |

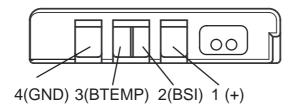

# Battery

| Li-ion battery pack BLB-2 is used in NHM-7. |      |  |  |

|---------------------------------------------|------|--|--|

| Nominal discharge cut-off voltage           | 3.1V |  |  |

| Nominal battery voltage                     | 3.6V |  |  |

| Nominal charging voltage                    | 4.2V |  |  |

#### Pin numbering of battery pack

| Signal name | Pin number | Function                                                               |

|-------------|------------|------------------------------------------------------------------------|

| VBAT        | 1          | Positive battery terminal                                              |

| BSI         | 2          | Battery capacity measurement (fixed resistor inside the battery pack)  |

| BTEMP       | 3          | Battery temperature measurement (measured by ntc resistor inside pack) |

| GND         | 4          | Negative/common battery terminal                                       |

#### BLB–2 battery pack pin order

# **Power Up and Reset**

Power up and reset is controlled by the UEM ASIC. NHM–7 baseband can be powered up in following ways:

1. Press power button which means grounding the PWRONX pin of the UEM

- 2. Connect the charger to the charger input

- 3. Supply battery voltage to the battery pin

- 4. RTC Alarm, the RTC has been programmed to give an alarm

After receiving one of the above signals, the UEM counts a 20ms delay and then enters it's reset mode. The watchdog starts up, and if the battery voltage is greater than Vcoff+ a 200ms delay is started to allow references etc. to settle. After this delay elapses the VFLASH1 regulator is enabled. 500us later VR3, VANA, VIO and VCORE are enabled. Finally the PURX (Power Up Reset) line is held low for 20 ms. This reset, PURX, is fed to the baseband ASIC UPP, resets are generated for the MCU and the DSP. During this reset phase the UEM forces the VCTCXO regulator on regardless of the status of the sleep control input signal to the UEM. The FLSRSTx from the ASIC is used to reset the flash during power up and to put the flash in power down during sleep. All baseband regulators are switched on at the UEM power on except SIM and VFLASH2 regulators which are controlled by the MCU. The UEM internal watchdogs are running during the UEM reset state, with the longest watchdog time selected. If the watchdog expires the UEM returns to power off state. The UEM watchdogs are internally acknowledged at the rising edge of the PURX signal in order to always give the same watchdog response time to the MCU.

# A/D Channels

The UEM contains the following A/D converter channels that are used for several measurement purpose. The general slow A/D converter is a 10 bit converter using the the UEM interface clock for the conversion. An interrupt will be given at the end of the measurement.

The UEM's 11–channel analog to digital converter is used to monitor charging functions, battery functions, voltage levels in external accessory detection inputs, user interface and RF functions.

When the conversion is started the converter input is selected. Then the signal processing block creates a data with MSB set to '1' and and others to '0'. In the D/A converter this data controls the switches which connect the input reference voltage (VrefADC) to the resistor network. The generated output voltage is compared with the input voltage under measurement and if the latter is greater, MSB remains '1' else it is set '0'. The following step is to test the next bit and the next...until LSB is reached. The result is then stored to ADCR register for UPP to read.

The monitored battery functions are battery voltage (VBATADC), battery type (BSI) and battery temperature (BTEMP) indication.

The battery type is recognized through a resistive voltage divider. In phone there is a 100kOhm pull up resistor in the BSI line and the battery has a pull down resistor in the same line. Depending on the battery type the pull down resistor value is changed. The battery temperature is measured equivalently except that the battery has a NTC pull down resistor in the BTEMP line.

KEYB1&2 inputs are used for keyboard scanning purposes. These inputs are also routed internally to the miscellaneous block. In NHM–7 KEYB1 input is used for flip detection.

The HEADINT and HOOKINT are external accessory detection inputs used for monitoring voltage levels in these inputs. They are routed internally from the miscellaneous block and they are connected to the converter through a 2/1 multiplexer.

The monitored RF functions are PATEMP and VCXOTEMP detection. PA-TEMP input is used to measure temperature of the RFIC, Hagar. VCXO-TEMP is not used in NHM–7.

# FM Radio

FM radio circuitry is implemented using highly integrated radio IC, TEA5757. Only few external components like filters, discriminator and capacitors are needed.

TEA5757 is an integrated AM/FM stereo radio circuit including digital tuning and control functions. NHM–7 radio is implemented as superheterodyne FM mono receiver. FM stage of the TEA5757 incorporates a tuned RF stage, a double balanced mixer, one pin oscillator and is designed for distributed IF ceramic filters. IF frequency is 10.7 MHz.

Channel tuning and other controls are controlled by the MCU. Reference clock, 75kHz, is generated by the UPP CTSI block.

FM radio circuitry is controlled through serial bus interface by the MCU SW. TEA5757 informs MCU when channel is tuned by setting *FMTuneX* signal to logic '0'.

#### **Digital Interface**

NOTE: *FMCtrlClk* needs to be set to logic '1' when data is not written or read. This is required for correct operation of the *FMTuneX* signal.

FM radio audio & antenna connections

# **IR Module**

The IR interface, when using 2.7V transceiver, is designed into the UEM. The IR link supports speeds from 9600 bit/s to 1.152 MBit/s up to distance of 1m. Transmission over the IR if half–duplex.

The lenght of the transmitted IR pulse depends on the speed of the transmission. When 230.4 kbit/s or less is used as a transmission speed, pulse length is maximum 1.63us. If transmission speed is set to 1.152Mbit/s the pulse length is 154ns according to IrDA specification.

# **Backup Battery**

Backup battery is used in case when main battery is either removed or discharged. Backup battery is used for keeping real-time clock running for minimum of 30 minutes.

Rechargeable backup battery is connected between UEM VBACK and GND. In UEM backup battery charging high limit is set to 3.2V. The cut-off limit voltage ( $V_{BUCoff-}$ ) for backup battery is 2.0V. Backup battery charging is controlled by MCU by writing into UEM register.

Polyacene SMD battery type is used. The nominal capacity of the battery is 0.2 mAh.

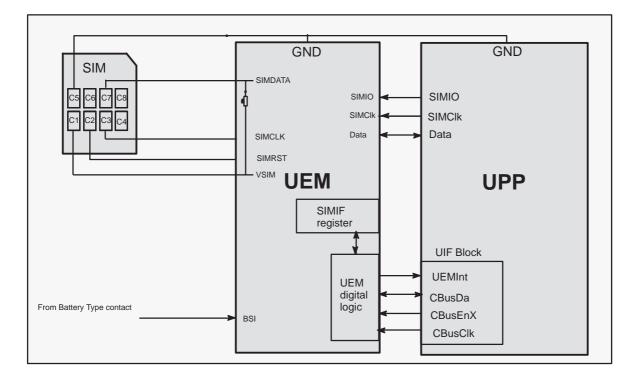

### **SIM Interface**

UEM contains the SIM interface logic level shifting. SIM interface can be programmed to support 3V and 1.8V SIMs. SIM supply voltage is selected by a register in the UEM. It is only allowed to change the SIM supply voltage when the SIM IF is powered down.

The SIM power up/down sequence is generated in the UEM. This means that the UEM generates the RST signal to the SIM. Also the SIMCardDet signal is connected to UEM. The card detection is taken from the BSI signal, which detects the removal of the battery. The monitoring of the BSI signal is done by a comparator inside UEM. The comparator offset is such that the comparator output do not alter state as long as the battery is connected. The threshold voltage is calculated from the battery size specifications.

The SIM interface is powered up when the SIMCardDet signal indicates "card in". This signal is derived from the BSI signal.

| Parameter                                | Variable | Min  | Тур | Max  | Unit |

|------------------------------------------|----------|------|-----|------|------|

| SIMCARDet, BSI comparator Threshold      | Vkey     | 1.94 | 2.1 | 2.26 | V    |

| SIMCARDet, BSI comparator Hysteresis (1) | Vsimhyst | 50   | 75  | 100  | mV   |

The whole SIM interface locates in two chip UPP and UEM.

The SIM interface in the UEM contains power up/down, port gating, card detect, data receiving, ATR–counter, registers and level shifting buffers logic. The SIM interface is the electrical interface between the Subscriber Identity Module Card (SIM Card) and mobile phone (via UEM device).

The data communication between the card and the phone is asynchronous half duplex. The clock supplied to the card is in GSM system 1.083 MHz or 3.25 MHz. The data baud rate is SIM card clock frequency divided by 372 (by default), 64, 32 or 16. The protocol type, that is supported, is T=0 (asynchronous half duplex character transmission as defined in ISO 7816–3).

The internal clock frequency from UPP CTSI block is 13 MHz in GSM. Thus to achieve the minimum starting SIMCardClk rate of 3.25 MHz (as is required by the authentication procedure and the duty cycle requirement of between 40% and 60%) then the slowest possible clock supplied to the SIM has to be in the GSM system clock rate of 13/4 MHz.

#### Buzzer

Buzzer is used to generate alerting tones and melodies to indicate incoming call. It is also used to generate keypress and warning tones for the user. Buzzer is controlled by PWM (Pulse Width Modulation) signal generated by the buzzer driver of the UEM. Target SPL is 100dB (A) at 5cm.

#### **Internal Microphone**

The internal microphone capsule is mounted in the bottom connector. Microphone is omnidirectional. The internal microphone is connected to the UEM microphone input MIC1P/N. The microphone input is asymmetric and microphone bias is provided by the UEM MIC1B. The microphone input on the UEM is ESD protected. Spring contacts are used to connect the microphone contacts to the main PCB.

# **NOKIA** PAMS Technical Documentation

UEM

#### UPP

UPP (Universal Phone Processor) is the digital ASIC of the baseband. UPP includes 8MBit internal RAM, ARM7 Thump 16/32–bit RISC MCU core, LEAD3 16–bit DSP core, ROM for MCU boot code and all digital control logic.

Main functions of the custom logic are:

- 1. Interface between system logic and MCU/DSP (Bodylf)

- 2. Clocking, timing, sleep and interrupt block (CTSI) for system timing control

- 3. MCU controlled general purpose USART, MBUS USART and general purpose IOs (PUP).

- 4. SIM card interface (SIMIf)

- 5. GSM coder (Coder)

- 6. GPRS support (GPRSCip)

- 7. Interfaces for keyboard, LCD and UEM (UIF)

- 8. Accessory interface for IrDA SIR, IrDA FIR and LPRF (AccIf)

- 9. SW programmable RF interface (MFI)

- 10. Programmable serial interface for Hagar RFIC (SCU)

- 11. Test interface (TestIf)

#### **Memory Block**

For the MCU UPP includes ROM, 2 kbytes, that is used mainly for boot code of MCU. To speed up the MCU operation small 64 byte cache is also integrated as a part of the MCU memory interface. For program memory 8Mbit (512 x 16bit) PDRAM is integrated. RAM block can also be used as data memory and it is byte addressable. RAM is mainly for MCU purposes but also DSP has also access to it if needed.

MCU code is stored into external flash memory. Size of the flash is 64Mbit (4096 x 16bit) The NHM–7 baseband supports a burst mode flash with multiplexed address/data bus. Access to the flash memory is performed as 16–bit access. The flash has Read While Write capabilities which makes the emulation of EEPROM within the flash easy.

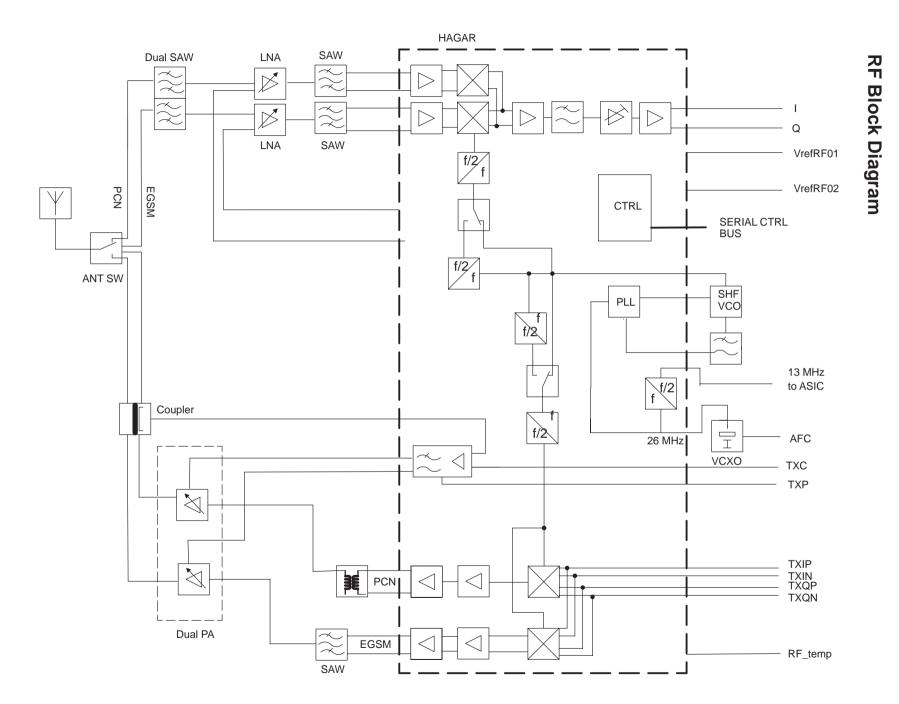

# **RF Module**

This RF module takes care of all RF functions of the engine. RF circuitry is located on one side (B–side) of the PCB.

EMC leakage is prevented by using a metal B–shield, which screens the whole RF side (included FM radio) of the engine. The conductive (silicon or metal) gasket is used between the PCB and the shield. The metal B–shield is separated to three blocks. The first one include the FM radio. The second block include the PA, antenna switch, LNAs and dual RX SAW. The last, but not least, block include the Hagar RF IC, VCO, VCTCXO, baluns and balanced filters. The blocks are divided on the basis that the attenuation between harmonics of the transmitter and the VCO signal (including Hagar IC) is a high (over 100dB). The VCO and TX outputs of the Hagar RF IC are located one another as far as possible. In order to guard against the radiated spurious inside blocks, the RF transmission lines are made with striplines after PA.

The baseband circuitry is located on the A–side of the board, which is shielded with a metallized frame and ground plane of the UI–board.

Maximum height inside on B–side is 1.8 mm. Heat generated by the circuitry will be conducted out via the PCB ground planes and metallic B–shield

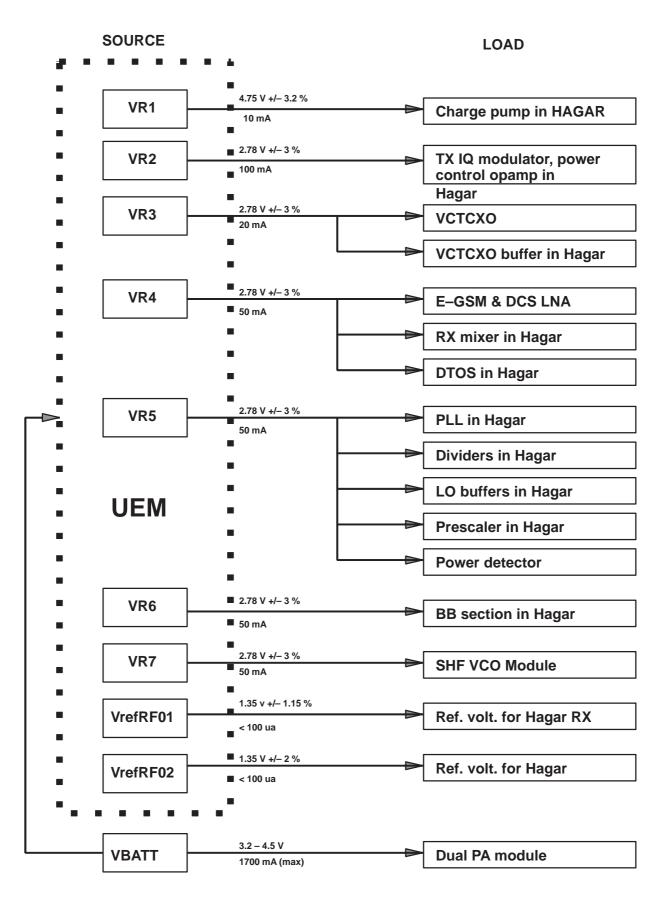

# **RF Frequency Plan**

# **DC characteristics**

#### Regulators

Transceiver has a multifunction power management IC on baseband section, which contains among other functions; 7 pcs of 2.78 V regulators and 4.8V up–switcher for charge pump.

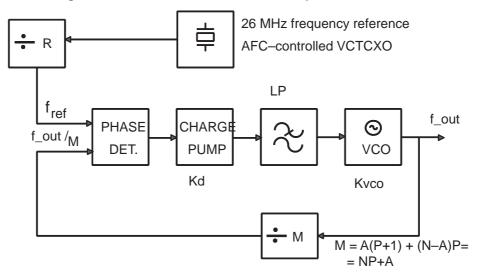

All regulators can be controlled individually with 2.78 V logic directly or through control register. In GSM direct controls are used to get fast switching, because regulators are used to enable RF–functions.

Use of the regulators can be seen in the Power Distribution Diagram. VrefRF01and VrefRF02 are used as the reference voltages for HAGAR RF–IC, VrefRF01 (1.35V) for bias reference and VrfeRF02 (1.35V) for RX ADC's reference.

Regulators (except VR2 and VR7) are connected to HAGAR. Different modes were switched on by the aid of serial bus.

List of the needed supply voltages :

| Volt. source | Load                              |

|--------------|-----------------------------------|

| VR1          | PLL charge pump (4,8 V)           |

| VR2          | TX modulator                      |

| VR3          | VCTCXO + buffer                   |

| VR4          | HAGAR IC (LNAs+mixer+DTOS)        |

| VR5          | HAGAR IC (div+LO–buff+prescaler), |

| VR6          | HAGAR (Vdd_bb)                    |

| VR7          | VCO                               |

| VrefRF01     | ref. voltage for HAGAR            |

| VrefRF02     | ref. voltage for HAGAR            |

| Vbatt        | PA                                |

#### Power Distribution Diagram

# **RF characteristics**

| Item                     | Values (E–GSM / GSM1800)   |

|--------------------------|----------------------------|

| Receive frequency range  | 925 960 MHz / 18051880 MHz |

| Transmit frequency range | 880 915 MHz / 17101785 MHz |

| Duplex spacing           | 45 MHz / 95 MHz            |

| Channel spacing          | 200 kHz                    |

| Number of RF channels    | 174 / 374                  |

| Power class              | 4 (2 W) / 1 (1 W)          |

| Number of power levels   | 15 / 16                    |

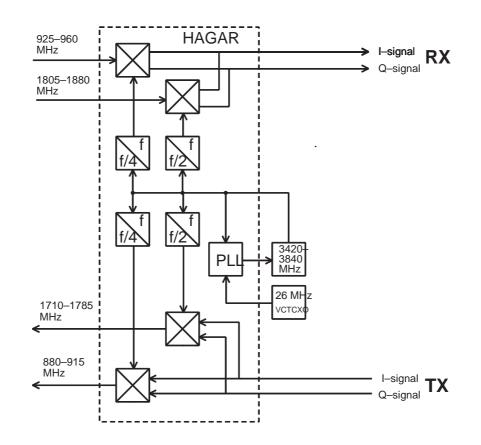

### **Transmitter characteristics**

| Item                             | Values (E–GSM/GSM1800)                  |  |

|----------------------------------|-----------------------------------------|--|

| Туре                             | Direct conversion, nonlinear, FDMA/TDMA |  |

| LO frequency range               | 35203660 MHz / 34203570 MHz             |  |

| Output power                     | 2 W / 1 W peak                          |  |

| Gain control range               | min. 30 dB                              |  |

| Maximum phase error ( RMS/peak ) | max 5 deg./20 deg. peak                 |  |

#### **Receiver characteristics**

| Item                                                           | Values, E–GSM/GSM1800                         |  |

|----------------------------------------------------------------|-----------------------------------------------|--|

| Туре                                                           | Direct conversion, Linear, FDMA/TDMA          |  |

| LO frequencies                                                 | 37003840 MHz / 36103760 MHz                   |  |

| Typical 3 dB bandwidth                                         | +/- 91 kHz                                    |  |

| Sensitivity                                                    | min. – 102 dBm (GSM1800 norm.cond. only)      |  |

| Total typical receiver voltage gain ( from antenna to RX ADC ) | 86 dB                                         |  |

| Receiver output level (RF level –95 dBm)                       | 230 mVpp, single–ended I/Q signals to RX ADCs |  |

| Typical AGC dynamic range                                      | 83 dB                                         |  |